STi5100 и STi5101 - однокристальные декодеры для цифровых абонентских ТВ приемниковНа страницах журнала [1] читатели уже знакомились с однокристальными декодерами цифровых ТВ сигналов STi5514, STi5516-Sti5518 семейства Omega фирмы STMicroelectronics. На этих ИМС было собрано огромное количество абонентских ТВ терминалов-приставок стандарта DVB. В продолжение этой темы автор рассматривает одну из последних разработок фирмы — ИМС STi5100 и STi5101, в основе которых лежит процессорное ядро ST20-C20x второго поколения.

История создания ИМСSTi5100

Фирма STMicroelectronics проанонсировала ИМС STi5100 в мае 2004 года. Эта микросхема включает в себя все функции семейства Omega, а также обеспечивает дополнительные функции, что позволяет использовать ИМС для цифровой обработки сигналов стандарта MPEG-2 и применять ее в спутниковых, эфирных, кабельных абонентских приставках, а также в ресиверах для IP-вещания.

В тот период фирма работала по двум направлениям:

–переход к использованию в качестве ядра нового 32-разрядного процессора ST20-С10х с новой системой команд;

–внедрение в производство новой HCMOS9-технологии (90,11 мкм).

По ряду причин новый технологический процесс был применен для выпуска спроектированного декодера на ядре предыдущего поколения ST-C20x.

Уменьшение числа активных элементов на кристалле привело к снижению потребляемой ИМС мощности, в то же время была увеличена ее тактовая частота до 243МГц. Как и у предшественников STi5514, STi5516 и Sti5517 [1], ядро ИМС STi5100 оперирует со 174 командами.

Значительным преимуществом новой ИМС (рис. 1) является поддержка его интерфейса USB2.0, позволяющего значительно увеличить скорость обмена и подключить большое количество внешних устройств. Имея в своем составе ядро, работающее на повышенной, по сравнению с серией Sti55xx, тактовой частоте до 243 МГц, ИМС позволяет работать с оперативной памятью стандарта DDR. Процессор ST20-С10х построен на основе архитектуры VL-RISC, разработанной фирмой HEWLETT PACKARD. В свою очередь, основой этой архитектуры послужила технология VLIW (Very Long Instruction Word), разработанная в конце 80-х годов фирмой MULTIFLOW. Новые быстродействующие процессоры обеспечивают декодирование сигналов как стандартной (SD), так и высокой (HD) разрешающей способности.

ИМС Sti5100 применяется совместно с QPSK-демодулятором STV0399, COFDM-демодулятором STV0360 или QAM-демодулятором STV0297/J — такой набор ИМС позволяет создавать недорогие терминалы для приема сигналов спутникового, наземного и кабельного цифрового ТВ соответственно. Кроме того, ИМС STi5100/1 используются в цифровых ТВ приемниках стандарта DVB-T и DVB-ресиверах с функцией PVR.

Функциональное описание и архитектура ИМС STi5100

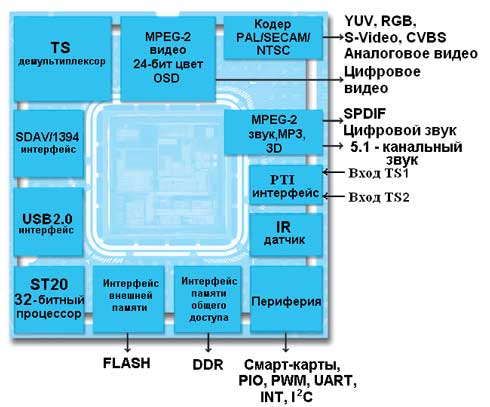

Рис. 1. Функциональный состав ИМС STi5100

Как и все ИМС семейства Omega, декодер STi5100 (рис. 1) имеет на своем кристалле демультиплексор транспортного потока TS, MPEG-2-декодеры видео- и аудиосигналов, 32-разрядный микроконтроллер (МК) семейства ST20, генератор OSD-графики (On Screen Display), цифровой DENC-видеокодер (Digital ENCoder) аналогового видеосигнала, цифроаналоговый преобразователь (ЦАП) звука, расширенную периферию. ИМС может обрабатывать одновременно два входных транспортных потока, а поэтому ее входной программируемый TS-интерфейс PTI (Programmable Transport Interface) имеет два независимых входа и два демультиплексора. Кроме того, в составе STi5100 имеются интерфейс HDDI (Hard Disk Drive Interface) и DES-скремблер для подключения HD-накопителя для записи программы, а также блок GPDMA для обеспечения функции прямого доступа к памяти общего назначения.

Процессорное ядро ИМС STi5100, внутренняя шина и внешние интерфейсы

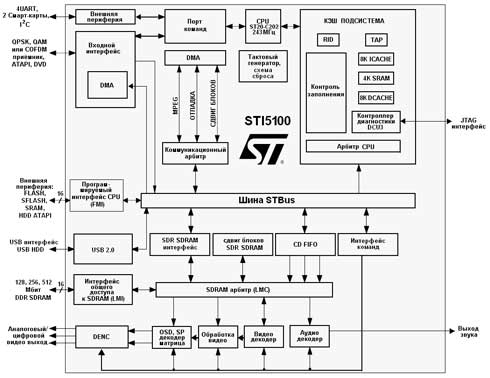

Архитектура ИМС Sti5100 показана на рис. 2. Основой ИМС является быстродействующее 32-разрядное RISC-ядро ST20-C202. Центральный процессор ST20C2+ осуществляет прямой доступ к встроенной статической памяти SRAM, служащей для хранения команд и данных.

Система памяти ИМС разделена на внутрикристальную и внешнюю. Внутрикристальная память имеет 8кбайт кеш команд (I-Cache), 8кбайт кеш данных (D-Cache) и 4кбайт SRAM. Последняя может быть сконфигурирована как кеш данных. Кеш команд и данных программно непосредственно адресуемые.

Рис. 2. Архитектура ИМС Sti5100

Уменьшение времени доступа к внешней памяти команд и данных осуществляется с помощью двунаправленной ассоциативной встроенной кеш-памяти, входящей вместе с SRAM в кеш — подсистему ядра. Доступ к внешней памяти обеспечивается программируемым CPU-интерфейсом посредством FMI-интерфейса внешней памяти (Flash Memory Interface) или LMI-интерфейса общего доступа (Local Memory Interface).

Статья доступна только в печатном варианте. Вы можете приобрести свежие номера Р&С или оформить подписку в редакции. |