Устройство и ремонт цифровых СТВ приемников "LUMAX SG-2000X" и "REDLINE RL-2005 FTA" (часть 2)Окончание. Начало в № 6, 2015 г.

При одновременном функционировании ведущего и ведомого ресиверов необходимо осуществлять прием сигналов с одинаковой поляризацией.

С выхода NIM-модуля сигнал TS в параллельном виде поступает на вход TS-роутера в составе U1. Тактовый сигнал частотой 27 МГц вырабатывается внутренним генератором ИМС U1 с опорным кварцевым резонатором U2. Из образцовой частоты внутренние схемы U1 формируют частоты для работы процессорного ядра и системной шины, внутренних узлов, внешней Flash- и SDR SDRAM-памяти. Сброс ресивера при включении осуществляется цепью R14 C26. Аппаратный сброс при ремонте можно активизировать, кратковременно замкнув выводы конденсатора C26.

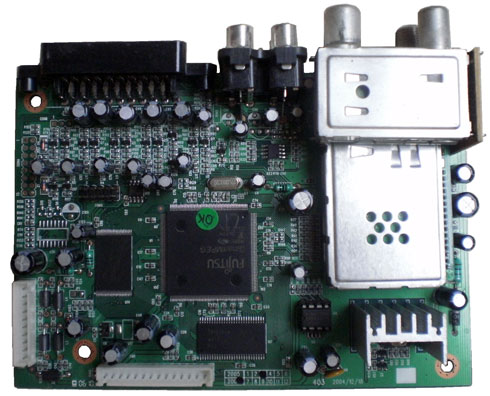

Рис. 10. Внешний вид главной платы YHGD7.820.403

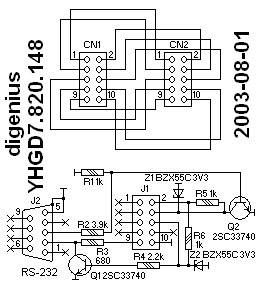

Ресивер управляется основным микроконтроллером ARC в составе ИМС U1. Ее UPI-интерфейс в данной схеме поддерживает параллельную Flash-память. Управляющая программа хранится во Flash-памяти U14 (S29AL008D70TF102 фирмы SPANSION) объемом 8 Мбит. Программу можно модифицировать с помощью интерфейса RS-232 без модификации загрузчика (Boot-секторов). Для сопряжения уровней интерфейса RS-232 и портов ввода/вывода U1 используется внешний модуль (см. рис. 11 и 12), который подключается к разъему CON5 главной платы.

Рис. 11. Принципиальная электрическая схема модуля сопряжения RS-232/U1

Если необходима полная модификация (перезапись) содержимого U2, используют метод программирования Flash-памяти через отладочный двухпроводный интерфейс DEBUG. Он подключается к контактам 5, 7, 10 разъема CON5.

К интерфейсу памяти общего доступа ИМС U1, работающему в 16-битном режиме, подключена ИМС динамического ОЗУ U7 (HY57V641620ET-H фирмы HYNIX) объемом 64 Мбит, работающая с тактовой частотой 133 МГц. Она арбитрированно используется декодерами видео- и аудиосигналов, управляющим процессором и цифровым кодером (DENC) ИМС U1.

Аналоговые сигналы видео и звука поступают на активные буферные усилители. ПЦТС обрабатывается усилителем на транзисторах Q11-Q14 и подается на разъемы CINCH и SCART. Сигналы R, G, B через буферные усилители на Q4, Q5, Q7-Q10 подаются на выход устройства через разъем SCART. Сигналы цифрового стереозвука по интерфейсу I2S через сдвоенный ЦАП U12 и активный ФНЧ на ОУ U13 поступают на разъемы CINCH и SCART.

Текущие настройки пользователя и данные, участвующие в процессе дескремблирования систем условного доступа, сохраняются во Flash-криптопамяти U4 (BMT9111). РЧ модулятор (переносит сигналы ПЦТС и звука на частоту одного из аналоговых ТВ каналов) устанавливается пайкой на основной плате (рис. 10) через переходную плату YHGD7.820/175A согласно схеме, показанной на рис. 13. Для питания ядра однокристального декодера U1 используется линейный стабилизатор U8, формирующий напряжение +1,8 В.

Полное содержание статьи доступно только в печатном варианте. Вы можете приобрести свежие номера Р&С или оформить подписку в редакции |